VHDL refers to as Verilog Hardware Description Language used as a programming tool for PLD’s/ Pal’s. The VHSIC Hardware Description Language (VHDL) is an industry standard language used to describe hardware from the abstract to concrete level. It defines the syntax but also defines very clear simulation semantics for each language construct. It provides extensive range of modelling capabilities. VHDL is used for coding models of analog and digital systems.

History/Formation of standard for VHDL:-

- In 1983 United States Department of Defence (DoD) established requirements for a standard VHSIC HDL.

- IEEE 1076/A VHDL Language Reference Manual (LRM) was released in May 1987 (By IEEE)

- Version B of the LRM was developed and approved by a committee of the IEEE standard hardware description language in December 1987

- Efforts for defining a new version of VHDL started in 1990 by a team of volunteers working under the IEEE Design Automation Standard Committee.

- In October 1992 a new VHDL referred to as VHDL’93 was completed and was released for review

- The VHDL standard presently used is referred to as VHDL 1076-1993.

Why to VHDL???

Some of us may wonder why VHDL so important and why I am emphasizing more on this software tool than any other, but the answer lies below.

- It has quick Time-to-Market

- It allows us to perform operations and computations with several nano-seconds.

- It allows designers to quickly develop designs requiring tens of thousands of logic gates and so on.

- It provides powerful high-level constructs for describing complex logic.

- It support’s modular design methodology and multiple levels of hierarchy.

- Device-independent designs that can be portable for multiple vendors.

- Users are given freedom to pick any synthesis tool, vendor, or device.

With such advantages and advance technology for complex computations this language is the foremost and best programming tool for synthesis and testing of electronic designs.

Features of VHDL:-

- CONCURRENCY – (It refers to execution of statements at the same time in parallel using various syntax and programming, as in hardware)

- SUPPORTS SEQUENTIAL STATEMENTS-(It supports sequential statements also and executes one statement at a time in sequence only.)

- SUPPORTS FOR TEST & SIMULATION- (To ensure that design is correct as per the specifications, the designer has to write another program known as “TEST BENCH” which helps in simulation virtually.)

- SUPPORTS FOR VENDOR DEFINED LIBRARIES

- SUPPORTS MULTIVALUED LOGIC

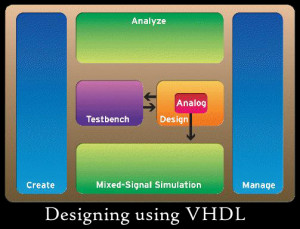

Designing using VHDL:-

For designing and implementing a hardware on FPGA, CPLD one can use various software tools (Xilinx ISE, Altera Quartus, Synopsys Synplify or Mentor Graphics HDL Designer, Leonardo Spectrum) which support VHDL. The Design Procedure comprises of creating a .vhd file which consists of the program code, containing the logic which is to be implemented on the hardware. After checking the syntax we can generate a schematic known as the RTL view, which specifies the design of the desired circuit in terms of gate level net-list. The same program is then dumped into the hardware alone with the connections of the various pin configuration using the place and route tool present in the respective software’s. Before doing the hardware synthesis, the software simulation is done where we get errors and faults on the virtually machine itself. The simulation is done using an appropriate Test bench program. An appropriate test bench for a particular circuit or VHDL code is generated by defining the inputs correctly. For example, for clock input, a loop process or an iterative statement is required. Simulation process is similar to waveform generation on a computer device.

this realy helped me to increase my interest and knowledge towards vlsi,vhdl.please allow me to follow your updates through email