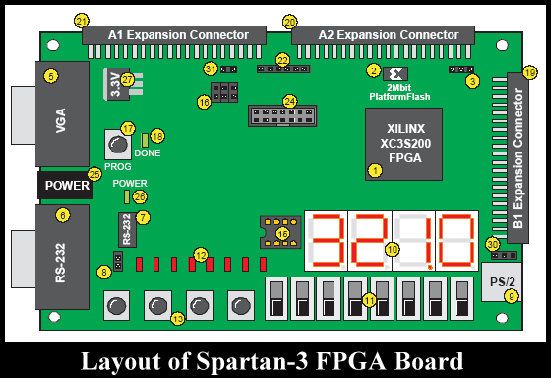

This article is base on a project executed on the Spartan-3 kit. Let’s get on with what exactly the article will consist of:

Arithmetic circuits form an important class of circuits in digital systems. Tremendous progress in the very large scale integration (VLSI) circuit technology has led to simplify, many complex circuits. Algorithms that seemed impossible to implement have now become attractive implementation possibilities for the future.

The article will explain about floating point addition, which will be carried out using comparison operation, shifting operation and adjustment of result. Now let’s see the basics of arithmetic operations and the VLSI applications.

i. Introduction:

Digital arithmetic operations are very important in the design of digital processors and application-specific systems. This means that there are unconventional as well as conventional computer arithmetic methods.

The notion of real numbers in mathematics is convenient for hand computations and formula manipulations. But, real numbers are not well-suited for general purpose computation, because their numeric representation as a string of digits expressed in base 10 can be very long or even infinitely long. In practice, computers store numbers with finite precision.

For example: π, e, and 2/5. Numbers and arithmetic used in scientific computation should meet a few general rules:

- Numbers should have modest storage requirements

- Arithmetic operations should be efficient to carry out

- The desired results obtained on one computer should

match with the results of the same computations on other computers.

The methods for representing numbers on computers have been established by the IEEE 754 standard to satisfy these basic goals. The arithmetic unit implementation has a 32-bit processing unit which allows various arithmetic operations such as, summation, taking square root, subtraction, product, division on floating point numbers.

Implementation of arithmetic unit will be a part of a computer system specially designed to carry out operations on floating point numbers. Some systems (particularly older systems, microcode-based-systems) can also perform various transcendental functions such as exponential or trigonometric calculations. Many embedded processors, especially older designs. Since, they do not have hardware support for floating-point operations. In most modern general purpose computer systems, one or more floating point units are integrated with the CPU. In the early days, some systems have implemented floating point via a coprocessor rather than as an integrated unit. In the microcomputer era is used to be generally a single microchip, but in early old systems it could be an entire circuit board or a cabinet. But not all computer architectures have hardware floating point unit.

Floating point operations are hard to implement on the FPGAs because of the complexity of their algorithms. Excessive chip area required, which is always limited in FPGAs. It becomes even more problematic if 32 bit floating point operations are required. we use the IEEE 754 standard for binary floating point arithmetic to implement a floating point adder on FPGAs in order to accommodate this requirement. We will start our discussion by briefly reviewing the IEEE 754 standard for binary floating point arithmetic and the generic representation of 32 bit floating point arithmetic in the next article.